First Check Power, Then Check Clocks

It was during my first job as a computer technician in high school that I developed the maxim: first check power, then check clocks.More

Digital IC design, design methodology and electrical engineering.

It was during my first job as a computer technician in high school that I developed the maxim: first check power, then check clocks.More

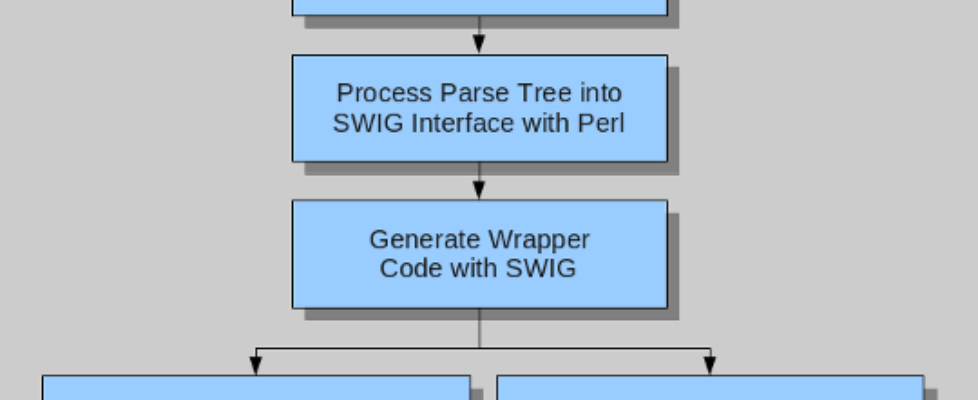

At DAC 2011 I gave a presentation on the architecture of oaScript at Si2’s OpenAccess Scripting Language Workshop.

Chip design is an iterative process. The design flow is run repeatedly as it is extended and refined into a program that can automatically build the entire chip. Your flow needs software to make sure that only the necessary steps are executed, in the correct order, on the correct data. Different hierarchical blocks must be constructed similarly, yet differently.

This is one of a series of articles on simple, specific techniques that will make your chip design flow easy to use. In this installment, I will explain how to control your chip design flow, and rules to keep it organized.More

When a user wants chip design data, a script or a log file, how do they find it? They look at the file and directory names. In fact, this may be the only documentation available.

As an IC design flow architect, proper file naming is the most important thing you can do to guide your users to the data they need. Further, you need to use safe names that can be used without transformation for any purpose, on any computing platform.More

When you read an SDC file from the command line, it works fine. When you read it using a Tcl procedure, it won’t work, because the global variables cannot be accessed. Here’s how to fix this annoying problem.

More

This is an old, old post, but over the years it continues to be one of my most popular pages. I leave it here in the hope that it is still useful. Please add your corrections or comment. –John

It is good design practice to use as few SDC files as possible. This post describes a way to create a single SDC file that can be used both before and after clock tree synthesis (CTS), and by both Cadence PKS and SoC Encounter.More